Hallo Gerd, Marius und alle die wissen wollen, warum man Jitter hören kann.

Von Gerd kam ja eine Steilvorlage:

derdoctor hat geschrieben:Ich habe allerdings auch ein leichtes Problem damit was sich da klanglich Auswirken soll.

Gut, man braucht einen Takt um die Daten nach der Übertragung durch ein Medium einwandfrei zurückzugewinnen.

Da die Flanken nicht endlos Steil sind kann der Takt nur Jitternd zurückgewonnen werden, allerdings sehe ich nirgends (habs auch selten so gemessen) das der Jitter die Ausmaße der eigentlichen Bitlänge erreicht und somit sollten die Flanken doch interpretiert werden können. Daher müsste meiner Meinung nach das Bit (und auch die folgenden) korrekt erkannt werden. Solange das der Fall ist, sollte es doch keine Probleme auf dem DAC geben, da der doch die unverfälschten Daten bekommt um sie wieder in ein Analogsignal zu wandeln.

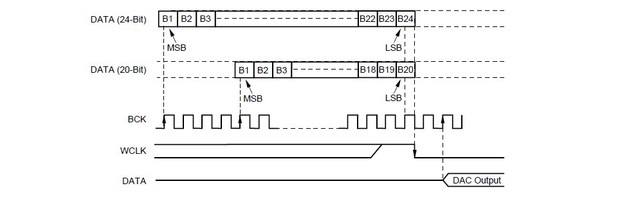

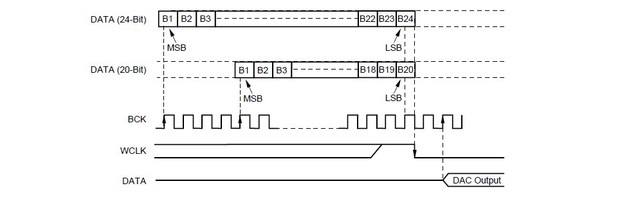

Für ein tieferes Verständnis der Zusammenhänge ist es unerlässlich, die Funktionsweise eines DA-Konverter-Chips etwas genauer zu verstehen. Schauen wir uns also mal genauer an, was in so einem DAC-Chip vor sich geht. Er kriegt folgende Signale (hier am Beispiel meines Lieblings-DAC PCM1704 von BurrBrown, aus dessen Datenblatt auch das Bild stammt):

Diese 3 Leitungen sind grob gesagt das, was in der Regel gemeint ist, wenn es um die mysteriöre, hier im Forum schon oft angesprochene I²S-Schnittstelle geht. Die bei Franz seinen (jetzt ausrangierten) Wandler mit dem Laufwerk verband. Bei Peter immer noch. Und in jedem CD-Player so in irgendeiner Form intern zu finden ist. Es gibt verschiedene Varianten, mal sind die Bits links bündig, mal links bündig mit Versatz (I²S oder auch Philips-Format genannt), mal rechts bündig zur Wordclock (Sony-Format wie hier gezeigt). Mal ist die steigende Flanke, mal die fallende eines Taktsignals von Bedeutung.

Es gibt also drei Signalleitungen, die erste beinhaltet die Daten (DATA), dann die Bitclock (BCK) und die Wordclock (WCLK). Die Bitclock sagt, zu welchem Zeitpunkt man in DATA schauen muss, ob es Null oder Eins ist. WCLK sagt, wann ein Datensatz anfängt. Oder, wie hier im Bild, wann das Ende ist. Egal, Hauptsache, man weiß, wo das MSB (das Bit mit dem meisten Gewicht) und das LSB (das Bit mit dem kleinsten Einfluss) ist. Mit Bitclock (immerhin 24,576MHz in meinem DAC) werden die Daten in ein Schieberegister geklopft. Beim ersten Taktschlag (wenn das Taktsignal von Null auf Eins wechselt) wird das LSB (Bit Nr. 24 im Bild oben) in die erste Speicherzelle des Schieberegisters geschrieben. Es besteht aus 24 Speicherzellen. Bei der nächsten positiven Flanke des Takts wird eins weiter geschoben, also B24 rückt auf Zelle 2 und B23 wird in Zelle 1 eingelesen. Und so weiter, bis alle 24 Bit stramm im Register stehen.

Bei einem Multibitwandler, wie ich ihn hier beschreibe, wird dieser Inhalt des Schieberegisters nun in einen Analogwert übersetzt. Jede dieser 24 Speicherzellen steuert eine Stromquelle. Zelle Nr. 1 (mit dem MSB, Bit Nr. 1) kann immerhin die Hälfte des maximal möglichen Stroms beisteuern. Zelle Nr. 2 ein Viertel, Nr. 3 ein Achtel und so weiter. Man macht das mit Stromquellen, weil man Ströme so einfach addieren kann - Stichwort Kirchhoffsche Knotenregel. Man braucht nur alle Stromquellen miteinander verbinden und schon hat man die Summe. Die 24 Stromquellen sind also mit den Bit-Werten gewichtet. Und jede hat einen Schalter (Transistor), der vom Wert der zugehörigen Speicherzelle des Schieberegisters gesteuert wird.

Die Frage ist nur - wann werden die Schalter für die Stromquellen gesetzt? Zum Beispiel könnte man das mit der fallenden Flanke von WCLK im Bild machen, da sind alle Werte ins Register eingelesen. So wird das z. B. beim PCM63 und anderen gemacht. Oder, man wartet, bis (elektrisch gesehen) Ruhe im Chip eingekehrt ist und macht das z. B. mit der übernächsten positiven Flanke von BCK, wie beim PCM1704.

Wurden alle Schalter (möglichst gleichzeitig) gesetzt, geht das Spiel von vorne los, der nächste Datensatz wird durch Register geschoben und überschreibt einfach die vorhergehenden Werte. Dann werden wieder alle Schalter gleichzeitig gesetzt, und so weiter. Im Rhythmus von WCLK.

Mit der Flanke des Taktsignals, entweder WCLK oder BCK, wird also der Zeitpunkt bestimmt, an dem sich der Analogwert ändert. Der Analogwert ist die Summe der 24 Stromquellen. Der Wert bleibt eingefroren, bis sich die Schalterstellung wieder ändert. Der Zeitpunkt der Taktflanke bestimmt also direkt den Zeitpunkt, wann sich der Wert im Analogsignal wiederfinden lässt.

Das Ausgangssignal ist also ein Strom, der 2hoch24 Abstufungen kennt. Das wird in eine Spannung gewandelt (die klangsensibelste Stelle im Analogteil eines DAC) und dann mit einem Tiefpass die Treppenstruktur entfernt.

Wenn die Taktflanken nun wackeln (Jitter), wackelt im gleichen Rhythmus der Ausgabezeitpunkt des Stroms, der Zeitpunkt also, zu dem die Schalter umgesetzt werden. Der wackelnde Takt bewirkt damit direkt eine (ungewollte) Änderung des Analogsignals. Würde der Takt zum Beispiel mit einer festen Frequenz von 1kHz hin- und her zittern, gäbe das direkt Seitenbänder im Abstand von 1kHz unter- und oberhalb des Nutzsignals, also käme zu einem gedachten Ton von z. B. 5kHz einer mit 4 und einer mit 6kHz dazu. Je nach Größe der zeitlichen Abweichung (wird in ns oder ps angegeben) mehr oder weniger stark in der Amplitude. Da der Takt aber in der Regel nicht mit einer festen Frequenz wackelt, sondern alle möglichen Jitterfrequenzen im Hörbereich vertreten sind, bewirkt der Jitter eine spektrale Verbreiterung jeder Nutzfrequenz, die abgespielt werden soll. Und so klingt es auch: Verschliffen und unsauber.

Ich hoffe, ich konnte das Geheimnis "warum kann man das denn überhaupt hören" ein wenig lüften.

Viele Grüße

Gert